Perkhidmatan Sehenti SON8 TPS7A8101QDRBRQ1 Dengan Cip Elektronik IC Asli Dan Baharu

Atribut Produk

| JENIS | PENERANGAN |

| kategori | Litar Bersepadu (IC) |

| Mfr | Alat Texas |

| Siri | Automotif, AEC-Q100 |

| Pakej | Pita & Kekili (TR) Pita Potong (CT) Digi-Reel® |

| SPQ | 3000 T&R |

| Status Produk | Aktif |

| Konfigurasi Output | Positif |

| Jenis Output | Boleh laras |

| Bilangan Pengawal Selia | 1 |

| Voltan - Input (Maks) | 6.5V |

| Voltan - Output (Min/Tetap) | 0.8V |

| Voltan - Output (Maks) | 6V |

| Keluar Voltan (Maks) | 0.5V @ 1A |

| Semasa - Output | 1A |

| Semasa - Diam (Iq) | 100 µA |

| Semasa - Bekalan (Maks) | 350 µA |

| PSRR | 48dB ~ 38dB (100Hz ~ 1MHz) |

| Ciri Kawalan | Dayakan |

| Ciri-ciri Perlindungan | Lebih Arus, Lebih Suhu, Kekutuban Songsang, Di Bawah Voltan Kunci Keluar (UVLO) |

| Suhu Operasi | -40°C ~ 125°C (TJ) |

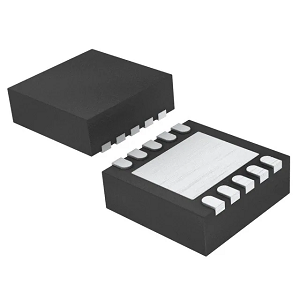

| Jenis Pemasangan | Lekapan Permukaan |

| Pakej / Kes | Pad Terdedah 8-VDFN |

| Pakej Peranti Pembekal | 8-ANAK (3x3) |

| Nombor Produk Asas | TPS7A8101 |

LDO, atau pengawal selia keciciran rendah, ialah pengawal selia linear keciciran rendah yang menggunakan transistor atau tiub kesan medan (FET) yang beroperasi di kawasan tepunya untuk menolak lebihan voltan daripada voltan masukan yang digunakan untuk menghasilkan voltan keluaran terkawal.

Empat elemen utama ialah Dropout, Noise, Power Supply Rejection Ratio (PSRR), dan Quiescent Current Iq.

Komponen utama: litar permulaan, unit pincang sumber arus malar, litar pemboleh, elemen pelarasan, sumber rujukan, penguat ralat, rangkaian perintang maklum balas dan litar perlindungan, dsb.

Prinsip Operasi

Litar asas LDO terdiri daripada pengawal selia siri VT, perintang pensampelan R1 dan R2, dan penguat perbandingan A

Sistem dikuasakan, jika pin daya berada pada tahap tinggi, litar dimulakan, litar sumber arus malar memberikan pincang kepada keseluruhan litar, voltan sumber rujukan cepat diwujudkan, dan voltan masukan yang tidak terkawal digunakan sebagai voltan daripada bekalan kuasa, voltan rujukan digunakan sebagai voltan masukan fasa negatif penguat ralat, rangkaian maklum balas perintang membahagikan voltan keluaran dan memperoleh voltan maklum balas, voltan maklum balas ini dimasukkan ke terminal arah yang sama bagi pembanding ralat, dan negatif Voltan maklum balas ini dimasukkan ke bahagian isotropik pembanding ralat dan dibandingkan dengan voltan rujukan negatif.Perbezaan antara kedua-dua voltan dikuatkan oleh penguat ralat untuk mengawal terus pintu elemen pelaras kuasa, dan output LDO dikawal dengan menukar keadaan pengaliran tiub pelaras, iaitu Vout = (R1 + R2)/ R2 × Vref

Pengatur linear keciciran rendah sebenar juga mempunyai fungsi lain seperti perlindungan litar pintas beban, penutupan voltan lampau, penutupan haba, perlindungan sambungan terbalik, dll.

Kelebihan, keburukan, dan status semasa

Pengawal selia linear Voltan Keluar Rendah (LDO) ialah kos rendah, hingar rendah, arus senyap rendah, beberapa komponen luaran, biasanya hanya satu atau dua kapasitor pintasan, dan mempunyai hingar sendiri yang sangat rendah dan Nisbah Penolakan Bekalan Kuasa (PSRR) yang tinggi.LDO ialah Sistem pada Cip (SoC) kecil dengan penggunaan diri yang sangat rendah.Ia boleh digunakan untuk kawalan saluran utama semasa dan mempunyai litar perkakasan bersepadu seperti MOSFET dengan rintangan dalam talian yang sangat rendah, diod Schottky, perintang pensampelan, dan pembahagi voltan, serta perlindungan lebihan arus, perlindungan lebih suhu, sumber rujukan ketepatan, penguat pembezaan, penangguhan, dll. PG ialah generasi baharu LDO dengan ujian kendiri untuk setiap keadaan keluaran dan bekalan kuasa selamat yang tertunda, yang juga boleh dipanggil Power Good, iaitu "power good atau power stable" .Banyak LDO memerlukan hanya satu kapasitor pada input dan satu pada output untuk operasi yang stabil.

LDO baharu boleh mencapai spesifikasi berikut: hingar keluaran 30µV, PSRR sebanyak 60dB, arus senyap 6µA, dan penurunan voltan hanya 100mV.Sebab utama peningkatan prestasi pengawal selia linear LDO ini ialah pengawal selia yang digunakan ialah MOSFET saluran P, yang dipacu voltan dan tidak memerlukan arus, mengurangkan arus yang digunakan oleh peranti itu sendiri dan penurunan voltan merentasinya.penurunan adalah kira-kira sama dengan hasil keluaran arus dan rintangan-pada.Penurunan voltan merentasi MOSFET adalah sangat rendah kerana rintangan padanya yang rendah.Pengawal selia linear biasa menggunakan transistor PNP.Dalam litar dengan transistor PNP, penurunan voltan antara input dan output mestilah tidak terlalu rendah untuk menghalang transistor PNP daripada memasuki tepu dan mengurangkan keupayaan output.

.png)

-300x300.png)